반응형

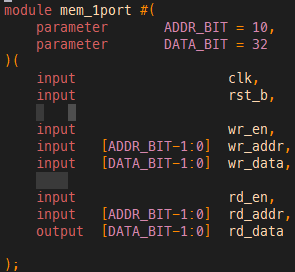

module 선언을 하다보면 동일한 기능인데 bit precision만 다른 경우가 있습니다.

verilog에서도 module 선언시에 parameter를 활용해서 이를 이용하는데요,

SystemC에서도 이렇게 설계가 가능한가 싶어 찾아보니 Template class를 사용하면 되는 것이었습니다.

평소에 C++을 사용하지 않다보니 문법을 찾아서 아래와 같이 설계를 변경해주었습니다.

사용은 기존에 memory를 8bit으로만 고정시켰었는데 이를 16bit으로도 사용하고 싶은 상태라 하면 아래와 같이 됩니다.

선언은 이렇게 해주고 사용하는 곳에서

이렇게 해주면 됩니다.

sc_signal 같은 경우는 바로 assign 하고 싶은데 무조건 신호들은 함수안에서 처리해야 하는 것 같습니다.

아직 systemC의 Error들이 어색해서 구글링하면서 배워가고 있습니다.

memory 입력을 R_in을 2번 write하는 걸로 해보았고 read했을 때 신호를 trace 하여 출력을 보면 아래와 같습니다.

우선 잘 입력되는 것은 확인했습니다.

이번에 알게 된 건데 verilog에서 concatenate 할 때 { } 안에 붙이고 싶은대로 붙인다면

SystemC에서는 ( ) 안에 저렇게 위에 쓴 것처럼 붙이고 bit를 나누고 싶다면 range를 쓰면 되는 것 같습니다.

이렇게 하면 입력의 하위 4bit만 복사하는 것이라 아래처럼 나오게 됩니다.

이걸 설계하다보니 클래스를 잘 쓰면 좋을 것 같다는 생각을 잠시 해봅니다......

'language > systemC' 카테고리의 다른 글

| [systemC] TLM 2.0 (0) | 2021.06.05 |

|---|---|

| [systemC] sc_vector 사용해보기 (0) | 2021.05.29 |

| [systemC] image filter를 위한 memory write/read (0) | 2021.05.23 |

| [systemC] SC_CTHREAD 사용 (0) | 2021.05.21 |

| [systemC] image 입력받기 (0) | 2021.05.19 |

댓글