반응형

기존에 사용해봤던 $signed 동작이 얼마나 chip에 많은 영향을 미치는지 확인해봅시다

해당 포스트는 FPGA 기반으로 한거라 정확하지는 않지만 이렇구나 정도만 알고있으면 될 것 같습니다.

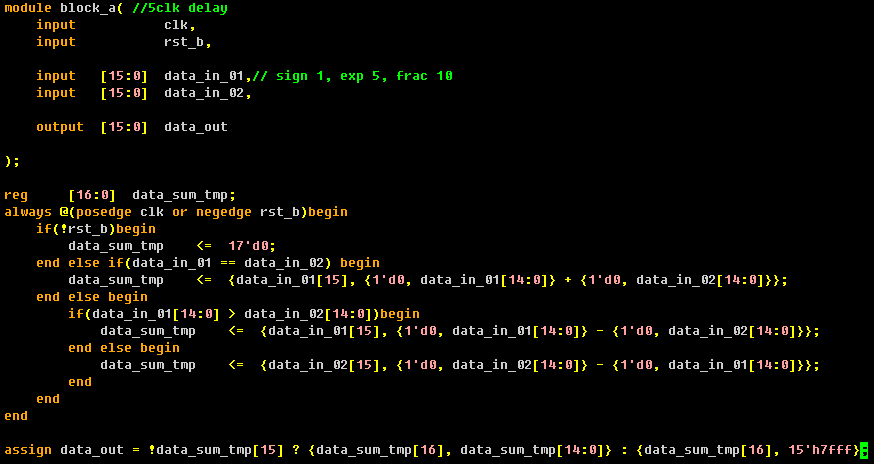

우선 단순 +/- 연산을 아래와 같이 case1, case2로 나누어서 설계합니다.(주석은 무시....)

case1은 부호를 따로 처리하는 unsigned 형식으로 설계, case2는 부호를 한번에 처리하는 signed로 설계했습니다

이걸 아래와 같이 한번에 돌리기 위해

이렇게 설계해서 돌리면 아래와 같은 FPGA 결과를 보여주는데요

signed로 casting 한게 더 좋게 보입니다.

하지만 현재 적용중인 code에서 연산 bit를 10bit씩 늘려주면 아래와 같이 바뀌는데요

이 결과를 보면 어떤게 무조건 적게 합성이되는 좋은 방법이다라는 것은 없는 것 같네요....

설계자의 경험과 tool의 계산 값을 확인하면서 설계하는게 가장 좋은 방법인 것 같습니다.

'language > Verilog' 카테고리의 다른 글

| [systemverilog] automatic keyword (0) | 2021.01.31 |

|---|---|

| [systemverilog] task 와 function (0) | 2021.01.31 |

| [verilog] $signed casting 사용 (0) | 2021.01.26 |

| [verilog] hardware realtime DCT (0) | 2021.01.26 |

| [verilog] 동일 logic LUT 비교 (0) | 2021.01.26 |

댓글