반응형

예전에 블로그 포스팅할때 정리해둘라고 했는데 아직도 정리를 못했습니다

우선 내용은 그대로 복사해놓고 집에서 시간나면 다른 tool로 돌려볼 예정입니다.

내용은 RGB to YCbCr을 두가지 방식으로 변환하였을 때의 LUT변화량 입니다

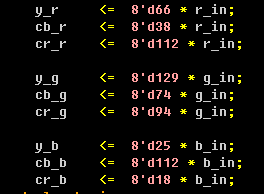

1. Case 1(한번에 연산)

이렇게 연산을 하면 simulation에서는 가능할지 몰라도 clock 주파수가 높아진다거나

target하는 timing에 meet를 하지못하는 case가 발생할 수도 있습니다.

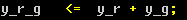

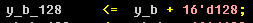

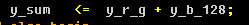

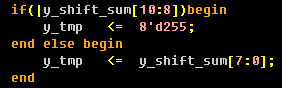

2. Case 2(clock 분배)

이렇게 설계하면 기존보다 5 clock정도의 delay가 생기지만 timing meet하기에는 유리한 조건으로 바뀌게 됩니다.

FPGA에서는 case 1처럼 해도 될 때도 있습니다만, 권고사항은 Case2 처럼 설계하는 방식이겠죠?

3. simulation result

결과는 위와 같이 나오게 되는데 timing조건은 안보고 단순히 LUT만을 확인한 수치로는

나누게 될 경우 좀 더 많은 LUT를 차지하게 된다가 나왔네요~

'language > Verilog' 카테고리의 다른 글

| [verilog] $signed casting 사용 (0) | 2021.01.26 |

|---|---|

| [verilog] hardware realtime DCT (0) | 2021.01.26 |

| [verilog] 16bit floating point hdl 구현(adder) (3) | 2021.01.26 |

| [verilog] 16bit floating point hdl구현(multiplier) (0) | 2021.01.25 |

| [verilog] memory 및 image filter 설계 (4) | 2021.01.24 |

댓글