반응형

저번 시간에 작성한 adder에 사용했던 코드들을 기반으로 multiplier를 구현해보려고 합니다

1. floating point multiplier 설계

multiplier는 over, underflow를 처리를 잘해줘야 하는 것으로 예상이 되는데

구현을 해야 convoltion 처리도 가능하므로

rtl code는 아래처럼 구성을 했습니다

이렇게 코드를 구성하면 나중에 warning이 뜨겠지만 그냥 결과만 보는 것이기에 그냥 사용했습니다

2. simulation result

simulation을 돌려서 나온 결과는

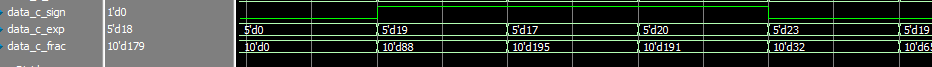

<input>

<output>

결과가 똑같이 나온것을 확인 할 수 있습니다

input : (19,88) → (17,195) → (20,191) → ...

output : (19,88) → (17,195) → (20,190) → ...

해당 결과를 보면 1개의 data를 처리하는 동안 task들이 멈춰져있는 것이 아니라

pipeline이 되도록 설계했는데 이 block은 3 clock의 delay가 발생했습니다.

저 위에 한번에 3개의 연산을 처리하는 부분이 timing maring이 있을지 여부는

tool을 돌려봐야 나올 것으로 예상됨..(나중에 올리겠습니다)

'language > Verilog' 카테고리의 다른 글

| [verilog] hardware realtime DCT (0) | 2021.01.26 |

|---|---|

| [verilog] 동일 logic LUT 비교 (0) | 2021.01.26 |

| [verilog] 16bit floating point hdl 구현(adder) (3) | 2021.01.26 |

| [verilog] memory 및 image filter 설계 (4) | 2021.01.24 |

| [verilog] image 입/출력 설계 (6) | 2021.01.23 |

댓글