CDC는 서로 다른 clock domain 간 data를 주고받는 것을 의미하는데

이때 clock이 다른 domain이라 함은 신호가 사용되는 주파수가 다르다는 것을 의미한다.

위의 그림처럼 각 영역에서는 clock이 다르기 때문에 metastable 상태에 빠지는 case가 발생할 수가 있다

metastable이란 준안정성이라고 번역이 되는데

이를 hardware 관점에서 분석하면

signal spec(setup time, hold time)에 맞지 않도록 신호가 전달되어

받는 쪽에서 0/1을 구분하지 못하는 것이라고 생각하면 된다

digital system에서는 0/1에 대한 구분이 명확해야 결과에 대한 신뢰성이 높은 것이기 때문에

metastable 한 조건이 생성되면 해당 system은 신뢰할 수가 없게 되어 설계과정에서 특별히 유의해야 한다

설계 시 해결할 수 있는 방법이 여러가지가 있다고 하는데

구글에서 참고한 자료를 기반으로 아래에 정리 해놓기로 함

참조 : www.edn.com/synchronizer-techniques-for-multi-clock-domain-socs-fpgas/

1. conventional f/f synchronizer

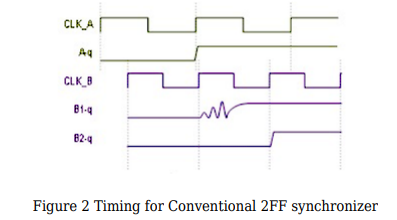

이렇게 일반적인 cdc 처리를 하게 될 경우 첫번째 B1이 metastable에 빠지는 timing diagram은 아래와 같다

2. toggle synchronizer

1번의 경우는 pulse 형태의 data는 전송하기가 어렵다고 나와있으며

(고속에서 저속으로 갈때, 생각해보면 저속은 clock이 더 오래 트리거 되는데 그 사이에 고속에서 바뀌어 버리면

수신 쪽에서는 바뀌었는지도 모르니깐)

이를 해결하기 위해 아래와 같은 구조로 대응한다고 되어있다

해당 회로의 timing diagram은 아래와 같다

timing diagram 보면 명확한 enable을 생성시키고 rising edge를 detect 하는 concept이다

3. handshaked based pulse synchronizer

1 clock pulse가 주기적으로 들어올 경우 처리를 못하는 case가 있으므로 이를 방지하기 위해

busy라는 신호를 생성해서 이 구간일 때는 data를 전송하지 않는 개념이며,

handshake라는 개념은 수신부의 data를 받고 보내는 형식이라서 그런 것으로 보인다

여기서는 뒤에 나오지는 않았지만 시간이 더 흘렀을 경우 A3-q가 0으로 떨어지는 순간부터는

'Busy'신호가 0으로 떨어지기 때문에 그때 sig-1을 발생시킬 수 있는 것으로 보인다

4. gray encodingd을 이용한 multi bit 송부

multi bit는 개별 bit에 위에 작성되었던 것들이 적용이 되는데 이렇게 될 경우 error가 발생할 수 있다고 한다

이를 막기 위해 gray encoding을 사용하는데 gray encoding은 값이 1만큼 차이 나면 실제 1bit만 서로 차이나는 인코딩

방식인데, 이 방식은 그렇다고 이해만 되고 설명을 봐도 아직.....

5. recirculation mux synchronization

enable과 data를 동시에 송부할 경우 아래와 같은 구조를 가짐

timing도 보면 B2-q와 M1이 동일한 시간대에 들어가게 되는 것을 확인할 수가 있다

6. handkshake synchronization

해당 방식은 지속적으로 보낼 필요가 없고 clock domain 간의 비율을 고려하지 않았을 때 사용

7. asynchronous FIFO synchronization

data들을 지속적으로 보낼 때 FIFO를 사용하여 data를 전송하는 방식이라고 한다

참조: https://www.edn.com/multiple-clock-domain-socs-addressing-structural-defects/

해당 내용을 정리하면 아래와 같다

1. convergence(수렴)

이걸 보면 conbinational logic을 통과하면서 생긴 delay가 logic마다 달라서 생겨서 C1, C2가 달라지고

이게 다른 domain으로 넘어가면서 생기는 현상(glitch발생)

이건 해결하려고 한번 더 해당 source clock으로 latch 하는 작업을 수행

2. divergence(분기)

domain이 바뀌면서 동일 신호가 분기가 되었는데 f/f 간 align이 맞지 않는 현상

이런 경우는 아래와 같이 하나로 합쳐서 진행 후 안정화된 이후에 분배하여 combinational logic 수행

3.reconvergence(재수렴)

동일한 source 도메인에서 발생한 신호가 각각 개별 synchronizer를 이용해서 같은 도메인으로 합쳐질 때 발생하는 경우

해결방법으로는 도메인을 넘어가서 하지 말고 보내기 전에 수행하는 것으로 해결한다

위와 같은 내용을 집에서 간략하게나마 simulation을 해보면 아래와 같다

우선 metastable 상태를 구현해보면

위의 코드를 실행하면 받는 clock이 더 느려서 제대로 전달이 되지 않은 것을 확인할 수가 있다

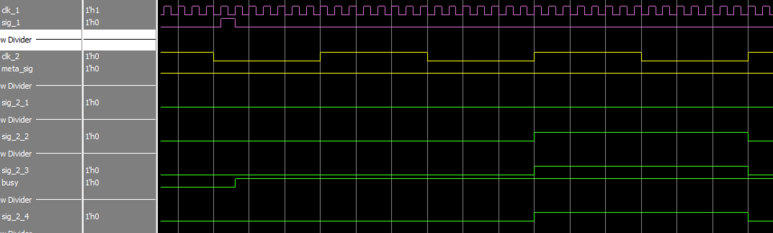

그 외에 자료에 나온 기법들을 이용하면 아래와 같이 나온다

1. conventional f/f synchronizer

2. toggle synchronizer

3. handshaked based pulse synchronizer

6. handkshake synchronization

위의 모듈들을 돌려보면 아래와 같이 제대로 신호는 나오는 것을 확인할 수가 있는데

(1,2,3,6 → 2_1, 2_2, 2_3, 2_4)

받는 clock을 엄청 느리게 하면 어떻게 될지 궁금해서 아래와 같이 바꿔봤는데

1.conventional f/f synchronizer 방식은 제대로 되지 않는 것을 확인할 수가 있다

실제 concept이랑 timing 만 봐도

단순히 f/f 몇 개 넣는 것만으로는 안 되는 것임을 확인했다.

나머지 3가지 방식은 송신 쪽에서 pulse가 발생했을 때 값을 유지하는 f/f을 가지고 있는 게 공통적인 특징이고

이렇게 유지된 값을 가지고 수신 쪽에서 만들어서 사용하는 것, 또는 ack를 어떻게 주냐 이런 식으로 나누어지는 것으로 특징이 생긴다.

'digital logic > knowlege' 카테고리의 다른 글

| 관성지연, 전달지연 (2) | 2020.10.20 |

|---|---|

| blocking vs non-blocking assignment(feat. race condition) (0) | 2020.10.19 |

| signed arithmetic (0) | 2020.10.16 |

| Clock gating (0) | 2020.10.14 |

댓글